一个高明的CAD工程师需要做的是:如何综合考虑各方意见,达到最佳结合点。以下为EDADOC专家根据个人在通讯产品PCB设计的多年经验,所总结出来的层叠设计参考,与大家共享。 PCB层叠设计基本原则 CAD工程师在完成布局(或预布局)后,重点对本板的布线瓶径处进行分析,再结合EDA软件关于布线密度(PIN/RAT)的报告参数、综合本板诸如差分线、敏感信号线、特殊拓扑结构等有特殊布线要求的信号数量、种类确定布线层数;再根据单板的电源、地的种类、分布、有特殊布线需求的信号层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。单板层的排布一般原则:A)与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层布线提供回流平面;B)所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻);C)主电源尽可能与其对应地相邻;D)尽量避免两信号层直接相邻;

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%。这有时很难做到,以 FR4板材上微带线的情况为例,我们计算一下。如果线宽8mil,线条和参考平面之间的厚度为4mil,特性阻抗为46.5欧姆。线宽变化到6mil后特性阻抗变成54.2欧姆,阻抗变化率达到了20%。反射信号的幅度必然超标。至于对信号造成多大影响,还和信号上升时间和驱动端到反射点处信号的时延有关。但至少这是一个潜在的问题点。幸运的是这时可以通过阻抗匹配端接解决问题。如果阻抗变化发生两次,例如线宽从8mil变到6mil后,拉出2cm后又变回8mil。那么在2cm长6mil宽线条的两个端点处都会发生反射,一次是阻抗变大,发生正反射,接着阻抗变小,发生负反射。如果两次反射间隔时间足够短,两次反射就有可能相互抵消,从而减小影响。假设传输信号为1V,第Y次正反射有0.2V被反射,1.2V继续向前传输,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假设6mil线长度极短,两次反射几乎同时发生,那么总的反射电压只有0.04V,小于5%这一噪声预算要求。因此,这种反射是否影响信号,有多大影响,和阻抗变化处的时延以及信号上升时间有关。研究及实验表明,只要阻抗变化处的时延小于信号上升时间的20%,反射信号就不会造成问题。如果信号上升时间为1ns,那么阻抗变化处的时延小于0.2ns对应1.2英寸,反射就不会产生问题。也就是说,对于本例情况,6mil宽走线的长度只要小于3cm就不会有问题。

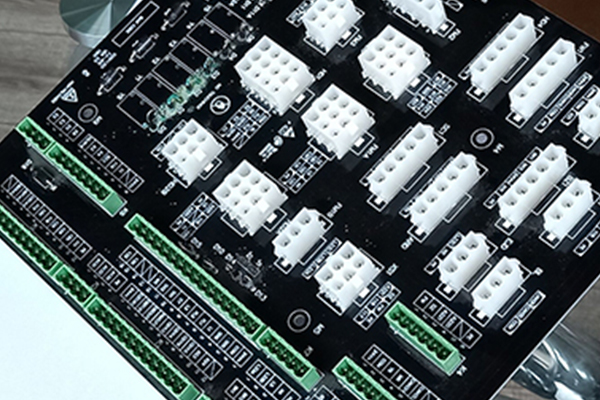

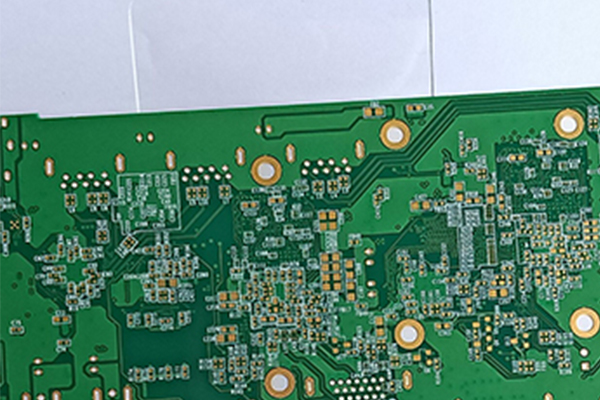

【第Y招】多层板布线高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 【第二招】高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 【第三招】高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 【第四招】高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。

香港专业FPC柔性版(一) 画好原理图很多工程师都觉得layout工作更重要一些,原理图就是为了生成网表方便PCB做检查用的。FPC柔性版加工厂其实,在后续电路调试过程中原理图的作用会更大一些。无论是查找问题还是和同事交流,还是原理图更直观更方便。另外养成在原理图中做标注的习惯,把各部分电路在layout的时候要注意到的问题标注在原理图上,对自己或者对别人都是一个很好的提醒。层次化原理图,把不同功能不同模块的电路分成不同的页,这样无论是读图还是以后重复使用都能明显的减少工作量。使用成熟的设计总是要比设计新电路的风险小。每次看到把所有电路都放在一张图纸上,一片密密麻麻的器件,脑袋就能大一圈。(二) 好好进行电路布局心急的工程师画完原理图,把网表导入PCB后就迫不及待的把器件放好,开始拉线。其实一个好的PCB布局能让你后面的拉线工作变得简单,让你的PCB工作的更好。每一块板子都会有一个信号路径,PCB布局也应该尽量遵循这个信号路径,让信号在板子上可以顺畅的传输,人们都不喜欢走迷宫,信号也一样。如果原理图是按照模块设计的,PCB也一样可以。按照不同的功能模块可以把板子划分为若干区域。模拟数字分开,电源信号分开,发热器件和易感器件分开,体积较大的器件不要太靠近板边,注意射频信号的屏蔽等等……多花一分的时间去优化PCB的布局,就能在拉线的时候节省更多的时间。

在基于信号完整性计算机分析的PCB设计方法中,最为核心的部分就是PCB板级信号完整性模型的建立,这是与传统的设计方法的区别之处。SI模型的正确性将决定设计的正确性,而SI模型的可建立性则决定了这种设计方法的可行性。目前构成器件模型的方法有两种:一种是从元器件的电学工作特性出发,把元器件看成‘黑盒子’,测量其端口的电气特性,提取器件模型,而不涉及器件的工作原理,称为行为级模型。这种模型的代表是IBIS模型和S参数。其优点是建模和使用简单方便,节约资源,适用范围广泛,特别是在高频、非线性、大功率的情况下行为级模型是一个选择。缺点是精度较差,一致性不能保证,受测试技术和精度的影响。另一种是以元器件的工作原理为基础,从元器件的数学方程式出发,得到的器件模型及模型参数与器件的物理工作原理有密切的关系。SPICE 模型是这种模型中应用最广泛的一种。其优点是精度较高,特别是随着建模手段的发展和半导体工艺的进步和规范,人们已可以在多种级别上提供这种模型,满足不同的精度需要。缺点是模型复杂,计算时间长。一般驱动器和接收器的模型由器件厂商提供,传输线的模型通常从场分析器中提取,封装和连接器的模型即可以由场分析器提取,又可以由制造厂商提供。在电子设计中已经有多种可以用于PCB板级信号完整性分析的模型,其中最为常用的有三种,分别是SPICE、IBIS和Verilog-AMS、VHDL-AMS。